Extending SDN and NFV with Deep Data-Plane Programmability

> Aki Nakao The University of Tokyo GFI 2013/11/19

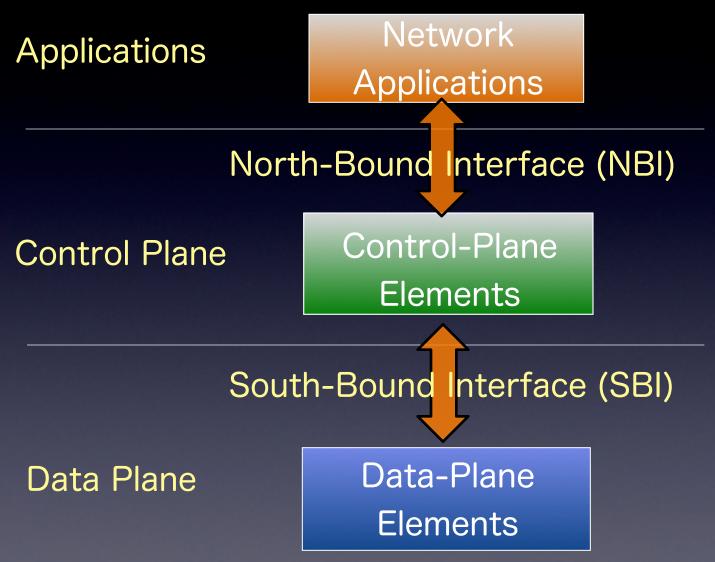

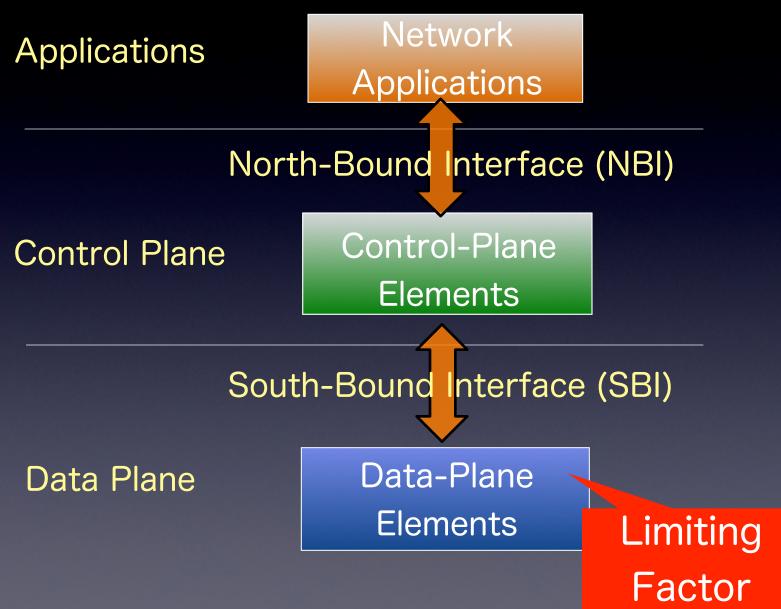

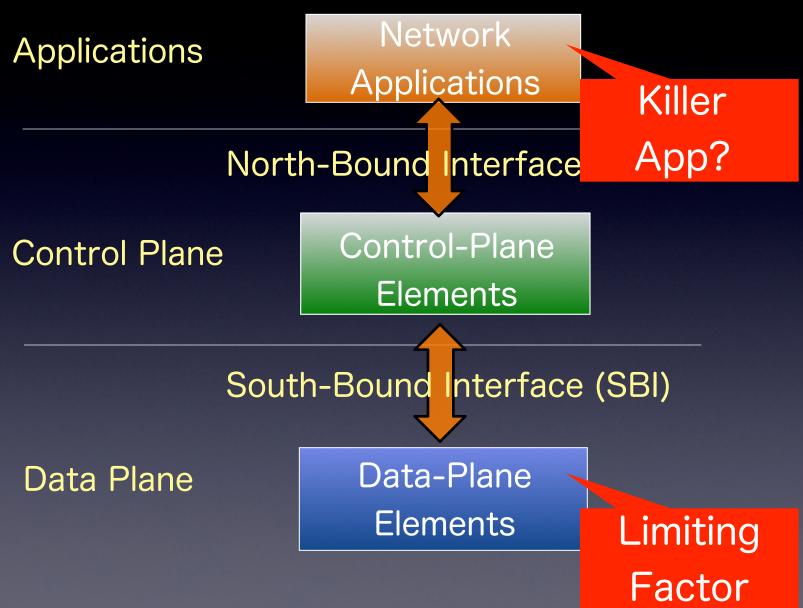

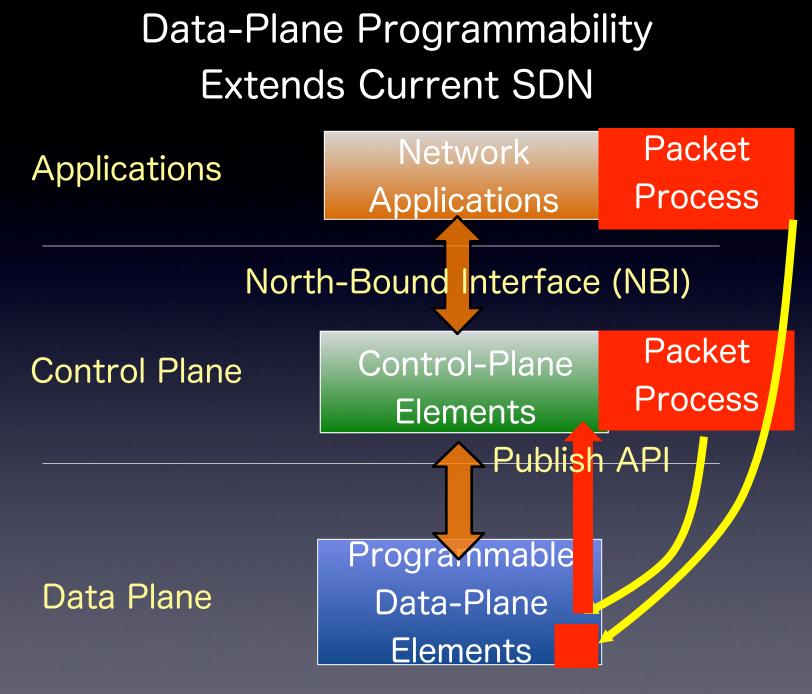

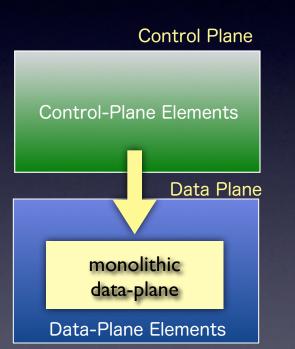

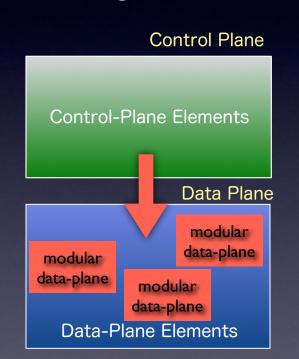

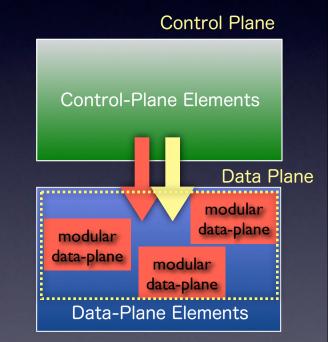

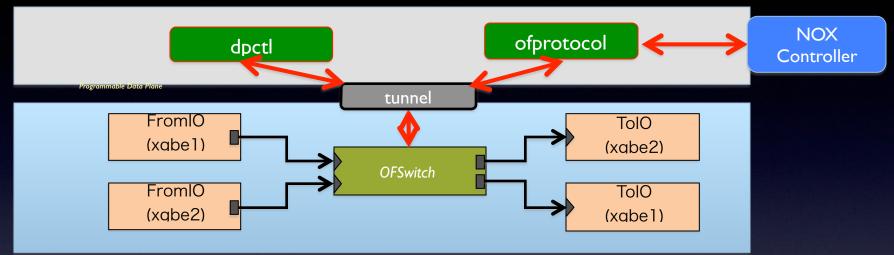

### **SDN** Architecture

### **SDN** Architecture

## **SDN** Architecture

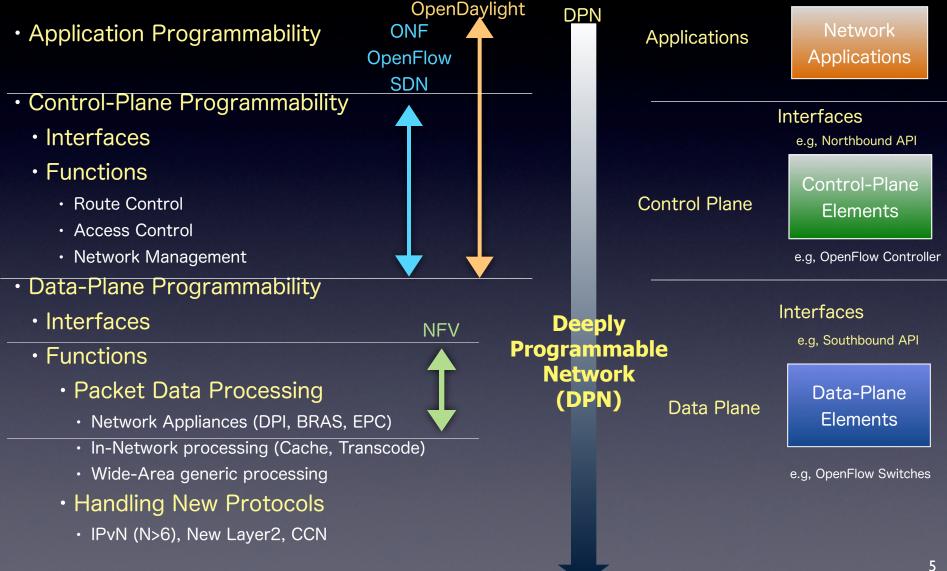

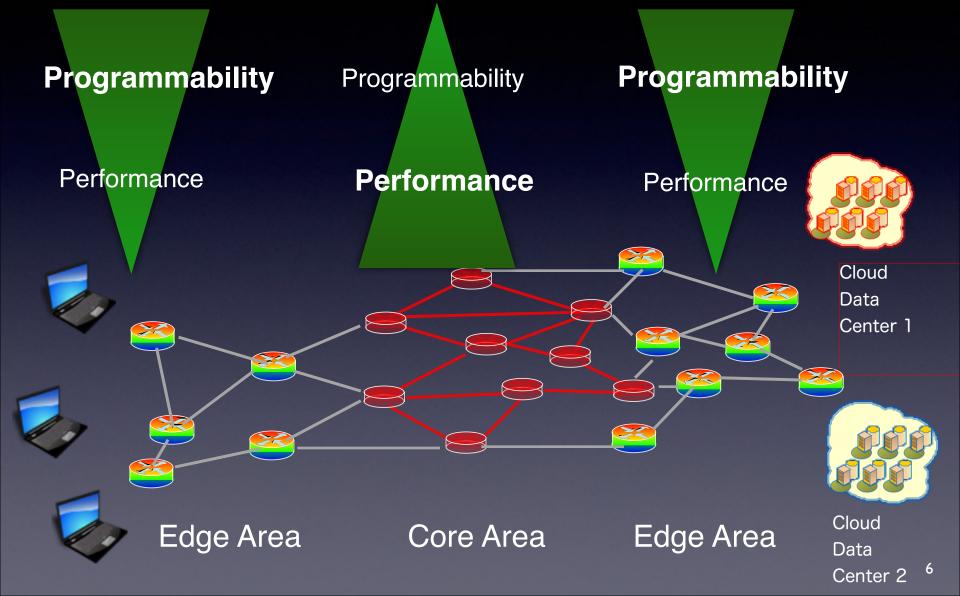

## **Deeply Programmable Network**

## Programmability / Performance Tradeoff

### Challenges

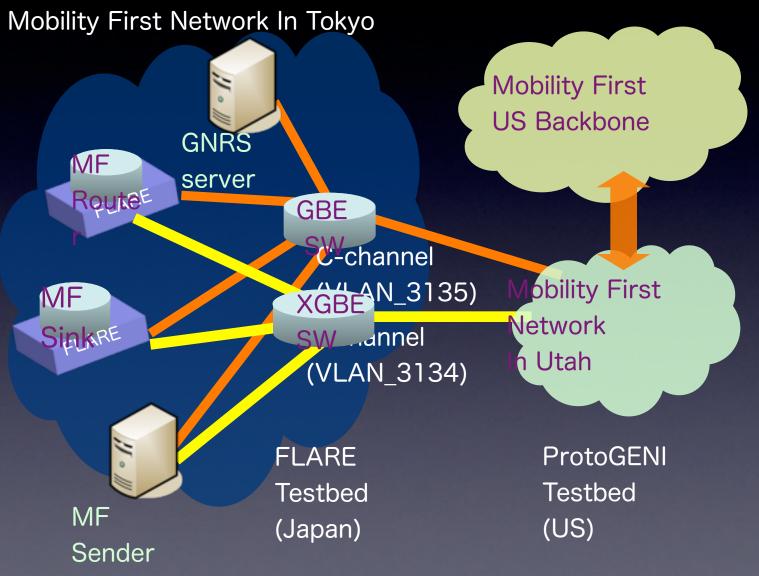

- Deep programmability

- (Reasonable) Performance

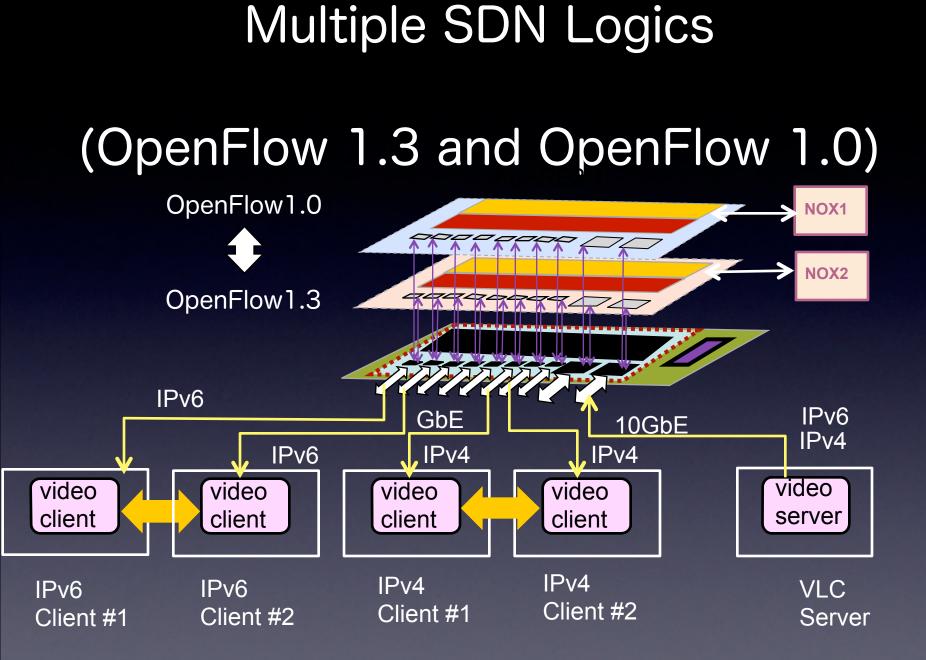

- Multiple Concurrent Logics

### FLARE's Approach to these challenges

- Linux(OSS)+Toy-Block Data Plane Construction

- Many-Core Network Processor + General Purpose Processor

- Virtualiztion/Resource Container

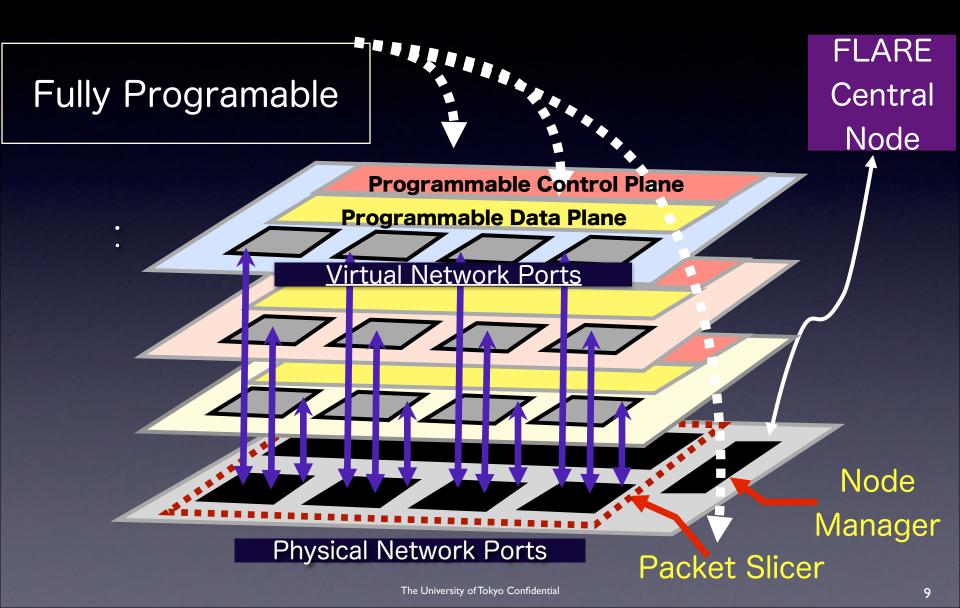

## FLARE Node Architecture

### **FLARE Node Implementation**

#### (board designed by NakaoLab)

36-72 cores

Hierarchical Resource Management<sup>(upto 100-200 cores in future)</sup> General Purpose Processor(s) Network Processor(s) ...and more types of processors

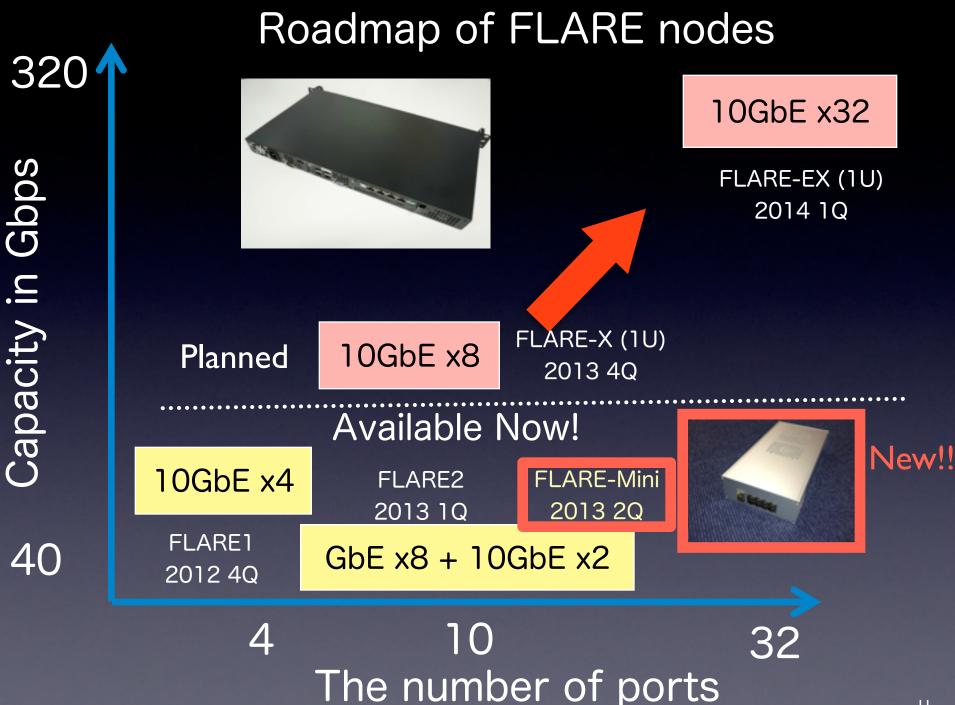

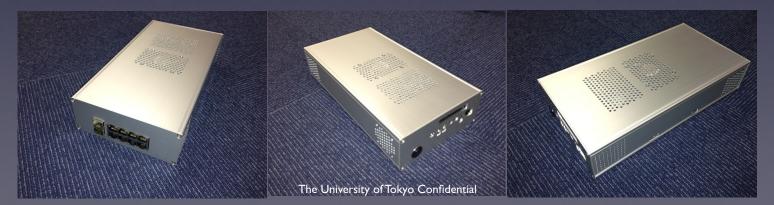

# FLARE Mini now available...

- Small Form Factor: 15cm x 6cm x 28cm

- Low power : 120W

- (Data Plane) Programmable node a graduate student can bring home and play with

- Capacity: 40G(current) ~ 80G (planned)

- Network I/F:10Gx2 + 1Gx8 (current) 10Gx8(planned)

- Preinstalled with network function elements that can be combined to enable arbitrary network functions e.g., OpenFlow 1.0/1.3, Packet Generator, Pcap Replay

## 8x1Gbe/2x10Gbe EEE FLARE Board Ver.1.1 UTokyo NakaoLab Feb.

### Data-Plane API and Toy Block Networking

SDN-style API

Hot Config Plug-in/out

Both API + Hot Config

e.g., e.g., openflow-style Object Oriented

## FLARE Programming Model in Sliver

#### Programmable Control Plane

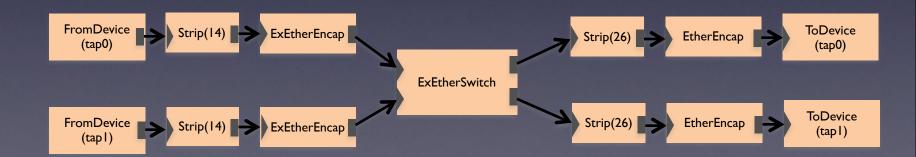

### Multi-Threaded Modular Programming e.g., Click Software Modular Router (multi-threaded)

Arbitrary switch logic(s) can be implemented

### L2 Programmability Extended (96bit) MAC switching

### Traditional Ethernet Frame:

DMAC (48bits) SMAC (48bits) Type IP PayLoad

### Extended Ethernet Frame with Extended MAC:

| DMAC (96bits) SMAC (96bits) | Туре | IP PayLoad |

|-----------------------------|------|------------|

|-----------------------------|------|------------|

### Prototype with Click

## PaF, PiF, PoF, Non-IP Protocol

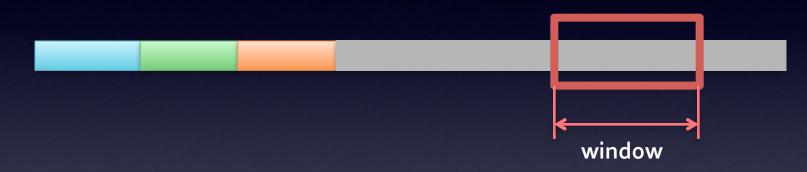

## Window-based Arbitrary Bit Matching

Arbitrary bit matching as in openflow pattern matcher is costly due to expensive memory operation per packet

Set a window to minimize per-packet memory operations Improve performance while keeping flexibility

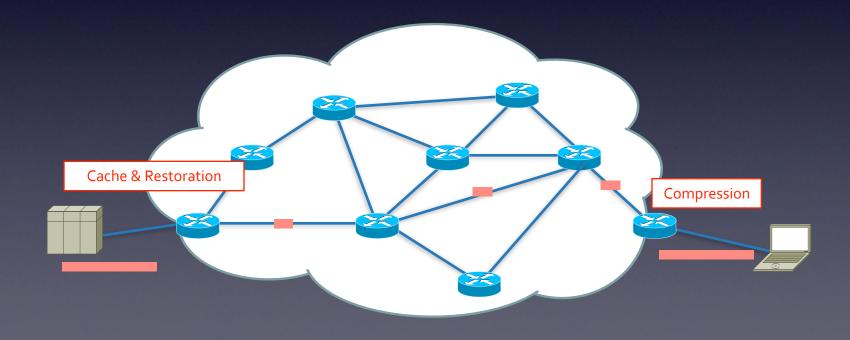

### YouTube Packet Cache

- Reduce cross-ISP redundant traffic

- Matching L7 (URL) not headers!

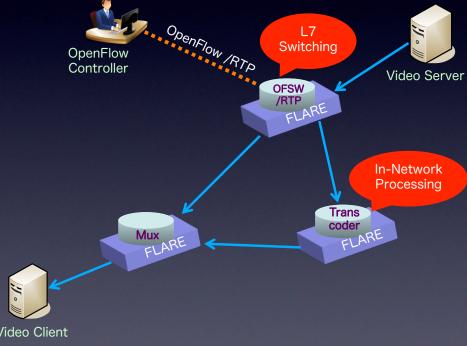

## L7 Switching and In-Network Processing

### L7 Switching

FLARE supports deeply programmable SDN solutions such as arbitrary-bits and arbitrary offset matching and definition of proprietary APIs achieving both flexibility and performance

In-Network Processing

Video transcoding can be preformed in real time on either D-plane (many-cores processor) or C-plane (Intel-CPU).

# Conclusion

- Deep Programmability refers to the extensive programmability including Control-plane, Data-plane (including non-IP handling), (re)defining APIs in SDN, etc.

- Deeply Programmable Network research encourages "clean-slate" thinking and redesigning the network and lifts the limitation in traditional networking and even in the current SDN.